### Qucs

# A Tutorial Getting Started with Digital Circuit Simulation

Mike Brinson

Copyright © 2006 Mike Brinson <mbrin72043@yahoo.co.uk>

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation. A copy of the license is included in the section entitled "GNU Free Documentation License".

#### Introduction

On 21 January 2006 Ques 0.0.8 was released by the Ques development team. This is the first version of the package to include digital circuit simulation based on VHDL. FreeHDL<sup>1</sup> being chosen as the VHDL engine. In the period following the release of Ques 0.0.8 there has been considerable activity centred around finding and correcting a number of bugs in the Ques digital simulation code. Many of these fixes are now included in the latest CVS code and will eventually form part of the next Ques release. This tutorial note is an attempt on my part to communicate to other Ques users a number of background ideas concerning the capabilities and limitations of the current state of Ques VHDL simulation. Much of the information reported here was assembled by the author while assisting Michael Margraf to test and debug the VHDL code generated by Ques. In the future, if there is enough interest in these notes, or indeed in Ques VHDL simulation in general, I will update them as the Ques digital simulation features are improved.

Ques digital simulation follows a complex set of steps that are mostly transparent to the software user. In step one, a schematic representing a digital circuit under test is drawn. This schematic consists of an interconnected group of Ques digital components, one or more user defined digital subcircuits (if required), and a copy of the digital simulation icon with the timing or truth table parameters set. In step two, the information recorded on a circuit schematic is converted into a text file containing VHDL statements. These describe the circuit components, their connection, and a testbench for simulating circuit performance. Next, FreeHDL is launched by Ques to convert the VHDL code file into a C++ source program. This is compiled to form an executable machine code simulation of the original circuit. Finally, Ques runs this program, collects signal data as digital signal events take place and displays signal waveforms as a function of time or digital data in a truth table format.

The VHDL code generated by Ques 0.0.8 is limited in its scope by the following factors:

- Digital gates are described by data flow concurrent statements.

- Flip-flops and the digital signal generator are described by process statements.

- Component connection wires (signals) can only be of type bit as defined in the standard VHDL library<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>The FreeHDL Project, http://www.freehdl.seul.org/.

<sup>&</sup>lt;sup>2</sup>Signal type bit only defines logic signals '0' and '1'. Care must be taken to ensure that signal

- Digital bus structures are not allowed in this release of the Ques package.

- Digital subcircuits can be drawn as schematics and associated with a symbol in a similar fashion to analogue subcircuits.

- Digital subcircuit pins can have type in, out, inout or analog. Ques treats pins of type analog the same as VHDL pin type inout.

- Once defined digital subcircuits may be placed and connected to other components on schematics.

- Multiple copies of the same digital subcircuit are allowed on a single schematic.

- Digital subcircuits may also be nested; nesting has been tested to a depth of four.

#### Simulating simple digital circuits

The most basic form of digital circuit that can be simulated is one consisting entirely of Ques predefined digital components drawn on a schematic having only one level of design hierarchy. The truth table for a simple combinational circuit of this type is shown in Table 1.

Output F can be expressed in sum of products Boolean form as

$$F = \overline{A}.\overline{B}.C + \overline{A}.B.\overline{C} + A.\overline{B}.C + A.B.\overline{C}$$

contention does not occur during simulation because the resulting logic state cannot be modelled with type bit. Signal contention can happen when two or more digital devices attempt to drive the same wire with logic '0' and logic '1' signals at the same time. Moreover, it is not possible to simulate the performance of tristate devices using VHDL signal type bit.

| А | В | С | $\mathbf{F}$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 0            |

| 0 | 0 | 1 | 1            |

| 0 | 1 | 0 | 1            |

| 0 | 1 | 1 | 0            |

| 1 | 0 | 0 | 0            |

| 1 | 0 | 1 | 1            |

| 1 | 1 | 0 | 1            |

| 1 | 1 | 1 | 0            |

Table 1: Truth table for a logic circuit with inputs A, B, C and output F.

On minimisation, using Boolean algebra or a Karnaugh map, output F becomes

$$F = A.C + B.\overline{C}$$

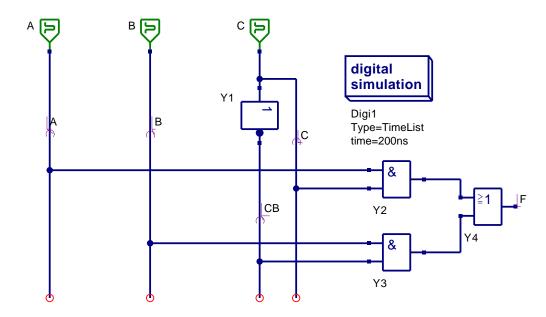

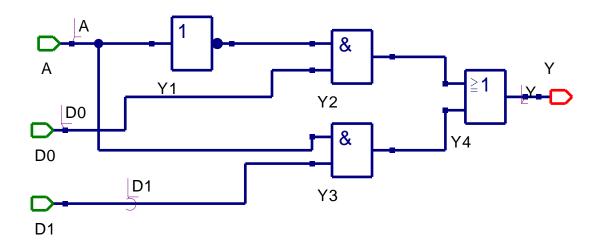

The schematic for example 1 is illustrated in Fig. 1. This diagram was constructed using the same techniques employed for drawing analogue schematics.

#### Notes on drawing digital schematics

- The only predefined Ques components that can be used to draw a digital circuit schematic are (1) the digital components listed in the digital components icon window, (2) the ground symbol, and (3) the digital simulation icon.

- A useful tip when drawing digital schematics is to adopt the matrix approach shown in Fig. 1. Input signals flow from top to bottom of the schematic and output signals are positioned on the right-hand side of a horizontal line. This makes checking the circuit schematic for errors much easier than the case where diagrams have wires connecting components in an unstructured way.

- Input and output wires (signals) should be given names consistant with the circuit being simulated, A, B, C and F in Fig. 1. If the signal wires are not named by the user, Qucs will allocate them different arbitrary names. This can make identification and selection of signals for display on an output waveform graph, and indeed checking for errors in a large circuit, much more difficult than it need be.

- Notice in Fig. 1 the international symbols for the logic gates are shown on the schematic.

Figure 1: Ques schematic for minimised logic function F.

#### VHDL code generated by Qucs

Clicking the Ques Simulate menu button (or pressing key F2) starts the simulation process. At an early phase in this process Ques writes a text file to disk that contains the VHDL code for the circuit being simulated. This file can be displayed by clicking on the **show last netlist** drop down menu or by pressing key F6. The VHDL code produced by Ques for the circuit shown in Fig. 1 is presented in Table 2.

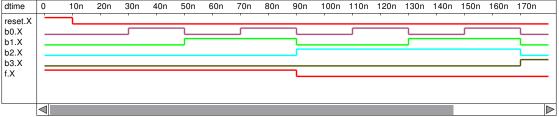

Signals identified by nnnet0 and nnnet1 in Table 2 have been allocated these names by Qucs; nnnet0 and nnnet1 are internal signal nets that are not named on the circuit schematic shown in Fig. 1. Fig. 2 illustrates the starting section of a typical Qucs digital functional waveform plot. This style of plot illustrates signal events without component delays. If required, signal delays can be specified for individual gates and other components (from the component *edit properties* menu). The VHDL code generated for components with delays will then reflect such changes, for example adding a 10 ns delay to signal CB in Table 2 generates VHDL code

$CB \ll not C after 10 ns;$

Readers will probably have observed that the Ques version number referred to in Table 2 VHDL listing is 0.0.9. This is the current CVS development version number. Ques 0.0.9 includes a number of important bug fixes. The remainder of these notes assume readers have downloaded, and recompiled, the latest CVS code

```

-- Ques 0.0.9 tut1\_ex1.sch

entity TestBench is

end entity;

use work.all;

architecture Arch_TestBench of TestBench is

signal CB, A, B, F, C,

nnnet0,

nnnet1 : bit;

begin

nnnet0 <= C and A;

nnnet1 <= CB and B;

CB \le not C;

A: process

begin

A \le '0'; wait for 40 ns;

A <= '1'; wait for 40 ns;

end process;

B: process

begin

B \le '0'; wait for 20 ns;

B <= '1';

wait for 20 ns;

end process;

F \ll nnnet1 or nnnet0;

C: process

begin

C <= '0'; wait for 10 ns;

C <= '1';

wait for 10 ns;

end process;

```

end architecture;

Table 2: VHDL code for the circuit shown in Fig. 1.

from Sourceforge.net<sup>3</sup>.

Figure 2: Digital functional waveforms for the circuit shown in Fig. 1.

#### Truth tables

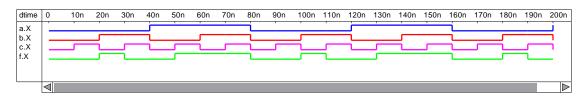

Truth tables are one of the most fundamental and convenient ways of displaying digital circuit data. Ques has a built-in facility that allows a truth table to be generated from a schematic drawing. This feature is particularly useful when checking minimised logic designs for errors. Lets consider a simple but instructive example: A logic circuit has four binary inputs A, B, C, and D, and one output P. Output P is logic '1' when inputs ABCD are numbers in the decimal sequence 3, 5, 7, 11 and 13. In Boolean sum of product form

$$P = \overline{A}.\overline{B}.C.D + \overline{A}.B.\overline{C}.D + \overline{A}.B.C.D + A.\overline{B}.C.D + A.B.\overline{C}.D$$

This simplifies to

$$P = D.(A.B + B \oplus C)$$

The schematic for the sum of products equation for P is shown in Fig. 3(a). Similarly Fig. 3(b) presents the schematic for a minimised P equation. Setting the digital simulation type to TruthTable, rather than TimeList, causes Ques on pressing key F2, to generate a truth table based on the information provided on a circuit schematic. The number of truth table inputs, and indeed outputs, correspond to the number of input generators and the number of named outputs. Truth tables for both schematics are given in Table 3(a) and 3(b). Comparing these two tables clearly indicates that they are not identical and moreover confirms that the minimised solution is not correct. Reworking the minimisation procedure points to the error being a missing signal inversion. The correct Boolean equation for P is

$$P = D.(A.B + B \oplus C)$$

<sup>&</sup>lt;sup>3</sup>Please note, Qucs Linux release 0.0.8 will normally simulate single hierarchy digital circuits without error. However, Qucs 0.0.8 does fail at the VHDL to C++ conversion phase if a schematic includes more than one ground symbol.

3(b): Schematic diagram for minimised equation P

| 3(a): | Truth | $\operatorname{table}$ | for | $\operatorname{sum}$ | of | products |

|-------|-------|------------------------|-----|----------------------|----|----------|

| equat | ion P |                        |     |                      |    |          |

| $\square$ |       | a.X | b.X | c.X | d.X | p.X |

|-----------|-------|-----|-----|-----|-----|-----|

|           | 00000 | 0   | 0   | 0   | 0   | 0   |

|           | 00001 | 0   | 0   | 0   | 1   | 0   |

|           | 00010 | 0   | 0   | 1   | 0   | 0   |

|           | 00011 | 0   | 0   | 1   | 1   | 1   |

|           | 00100 | 0   | 1   | 0   | 0   | 0   |

|           | 00101 | 0   | 1   | 0   | 1   | 1   |

|           | 00110 | 0   | 1   | 1   | 0   | 0   |

|           | 00111 | 0   | 1   | 1   | 1   | 1   |

|           | 01000 | 1   | 0   | 0   | 0   | 0   |

|           | 01001 | 1   | 0   | 0   | 1   | 0   |

|           | 01010 | 1   | 0   | 1   | 0   | 0   |

|           | 01011 | 1   | 0   | 1   | 1   | 1   |

|           | 01100 | 1   | 1   | 0   | 0   | 0   |

|           | 01101 | 1   | 1   | 0   | 1   | 1   |

|           | 01110 | 1   | 1   | 1   | 0   | 0   |

| $\nabla$  | 01111 | 1   | 1   | 1   | 1   | 0   |

3(b): Truth table for minimised equation P

|   |          |       | a.X | b.X | c.X | d.X | p.X |

|---|----------|-------|-----|-----|-----|-----|-----|

|   |          | 00000 | 0   | 0   | 0   | 0   | 0   |

|   |          | 00001 | 0   | 0   | 0   | 1   | 0   |

|   |          | 00010 | 0   | 0   | 1   | 0   | 0   |

|   |          | 00011 | 0   | 0   | 1   | 1   | 1   |

|   |          | 00100 | 0   | 1   | 0   | 0   | 0   |

|   |          | 00101 | 0   | 1   | 0   | 1   | 1   |

|   |          | 00110 | 0   | 1   | 1   | 0   | 0   |

|   |          | 00111 | 0   | 1   | 1   | 1   | 0   |

|   |          | 01000 | 1   | 0   | 0   | 0   | 0   |

|   |          | 01001 | 1   | 0   | 0   | 1   | 0   |

|   |          | 01010 | 1   | 0   | 1   | 0   | 0   |

|   |          | 01011 | 1   | 0   | 1   | 1   | 1   |

|   |          | 01100 | 1   | 1   | 0   | 0   | 0   |

|   |          | 01101 | 1   | 1   | 0   | 1   | 1   |

|   |          | 01110 | 1   | 1   | 1   | 0   | 0   |

| ľ | $\nabla$ | 01111 | 1   | 1   | 1   | 1   | 1   |

#### **Digital subcircuits**

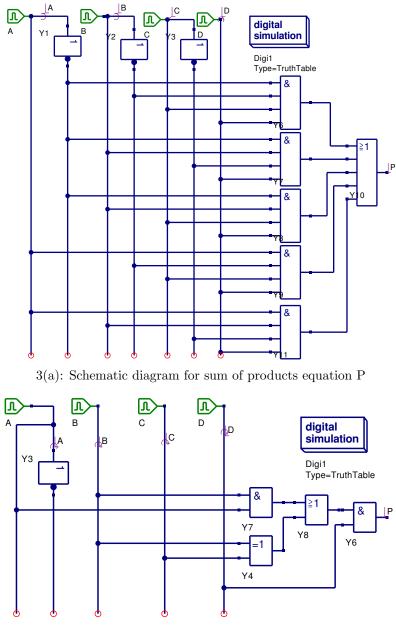

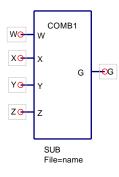

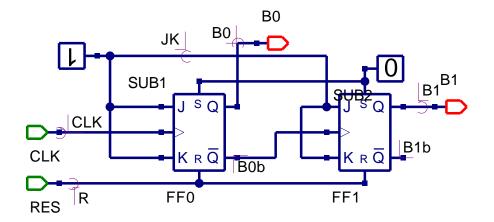

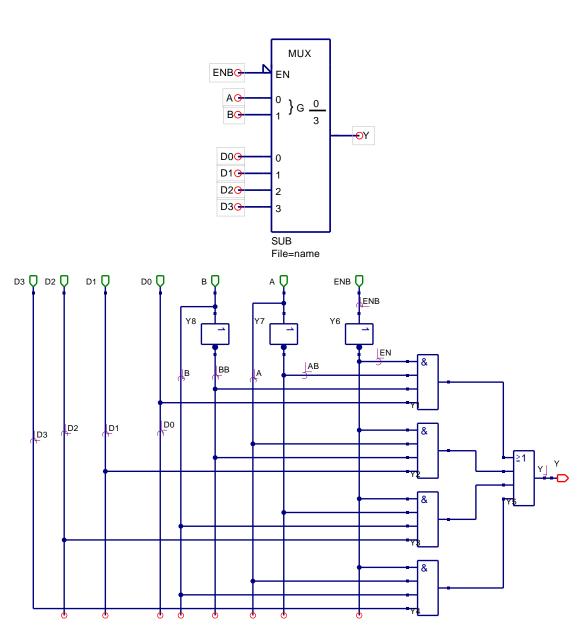

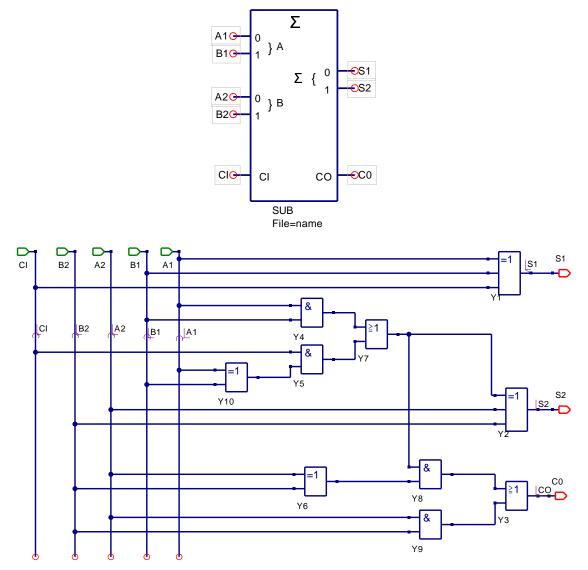

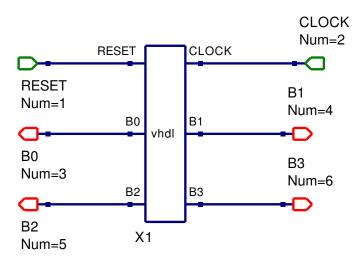

Although it is possible to draw complex schematic diagrams using only the predefined digital components supplied with Qucs, this technique can be extremely tedious, and is of course, prone to error. When drawing large schematics we require a design procedure that naturally subdivides groups of digital components into self contained units. These units can then be treated in the same way as basic digital components when placing and connecting them on a schematic drawing. In the world of analogue and digital circuit design such units are often called subcircuits.<sup>4</sup> A subcircuit is defined by three major attributes plus a number of other properties. The major attributes are, firstly a digital circuit that defines circuit function, secondly a circuit symbol that depicts a circuit in a higher level of a design hierarchy, and thirdly the subcircuit input/output pins shown on the subcircuits. It is best demonstrated by considering an example, signal path delays. The process for generating digital subcircuits is identical to that used for analogue subcircuits. It is best demonstrated by considering an example. Figure 4 shows the schematic for a four input combinational circuit.

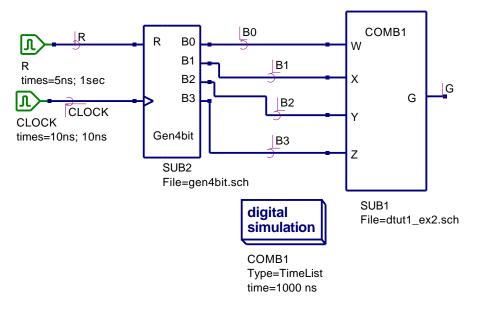

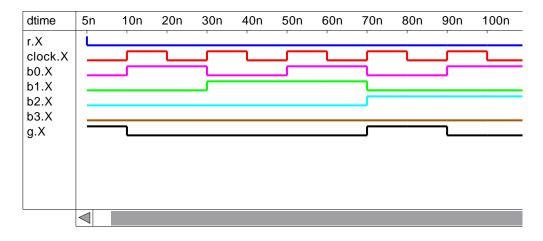

After drawing a subcircuit schematic, input and output<sup>5</sup> pins are attached to signal ports. Input port pins of type in are shown on circuit diagrams as a green symbol, signals W, X, Y, and Z, in Fig. 4. Ouput port pins of type out are coloured red, signal G in Fig. 4. Signal flow through a port is indicated by the direction of the port symbol arrow head. Input/output signals, and any other signals that need to be easily identified, are also named. Once the subcircuit schematic is complete, pressing key F3 causes Ques to generate a subcircuit symbol. The drawing tools listed as icons in the Ques paintings window can be used to edit Ques generated subcircuit symbols. The input/output port pins on a subcircuit symbol have the same type and name as those on the original subcircuit schematic. Fig. 5 shows the finished symbol for subcircuit COMB1. In these notes, symbol outlines are shown drawn in accordance with the international code for logic symbols<sup>6</sup>. To test our new subcircuit we place it's symbol on a blank drawing sheet and apply test signals to the input pins and observe the signals at the output pin. Fig. 6 shows a typical test circuit. Subcircuit Gen4bit generates a 4 bit test pattern synchronised

<sup>&</sup>lt;sup>4</sup>The circuit simulator SPICE is a well known example of a widely used CAD program that makes extensive use of subcircuits in circuit design.

<sup>&</sup>lt;sup>5</sup>Qucs 0.0.8 has a bug which causes a VHDL compile error when subcircuit pins are specified as type out. A work around for this bug is to specify subcircuit output pins as type analog. The Qucs routines that generate the circuit VHDL code convert pin type analog into VHDL type inout. FreeHDL is then able to compile the generated VHDL code without error. This bug has been corrected in Qucs 0.0.9.

$<sup>^{6}</sup>$  Ian, Kampel, A practical introduction to the new logic symbols, Butterworths, 1985, ISBN 0-408-01461-X.

Figure 4: Combinational logic circuit with inputs W, X, Y, Z, and output G.

to the input of a digital clock. The specification for Gen4bit is given in the next section of these notes<sup>7</sup>. The test pattern waveform and output signal G are shown plotted as a function of time in Fig. 7.

$<sup>^7 \</sup>rm Subcircuit$  Gen4bit includes other nested subcircuits. Ques 0.0.8 has a bug that causes VHDL compile errors with some configurations of nested subcircuits. This has been fixed in version 0.0.9.

Figure 5: Ques symbol for a logic circuit with inputs W, X, Y, Z, and output G.

Figure 6: Test schematic for a logic circuit with inputs W, X, Y, Z, and output G.

Figure 7: Digital functional waveforms for a logic circuit with inputs W, X, Y, Z, and output G.

#### Building a digital component library

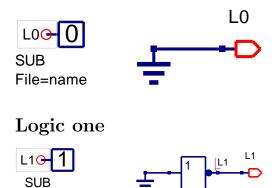

The Ques graphical user interface includes good project handling features. Combining these features with the Ques subcircuit capabilities provides all the tools required for the development of a library of common digital components. Such a library can be stored in a master project and the individual component files imported into other projects when required. Here are a few components that I developed during a recent series of tests aimed at detecting bugs in the VHDL code generated by Ques.

#### Logic zero

File=name

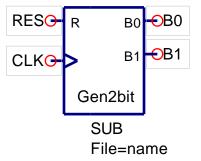

#### G2bit - 2 bit pattern generator

G4bit - 4 bit pattern generator

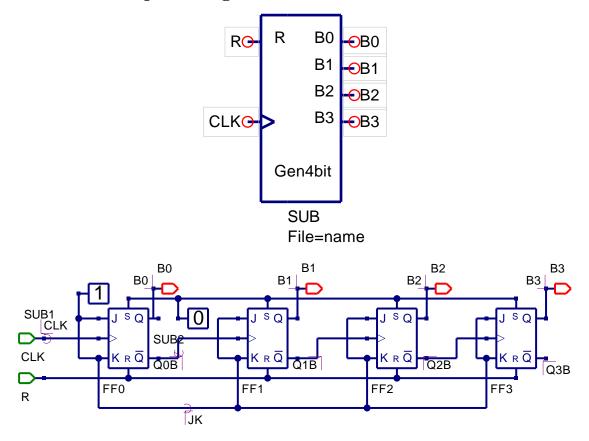

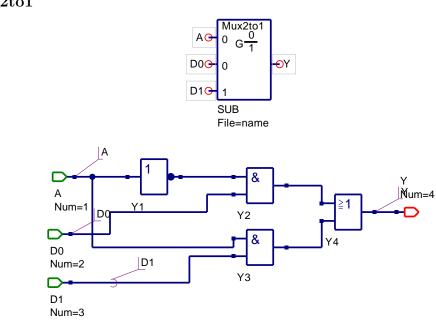

#### MUX2to1 - 2 input to 1 output multiplexer

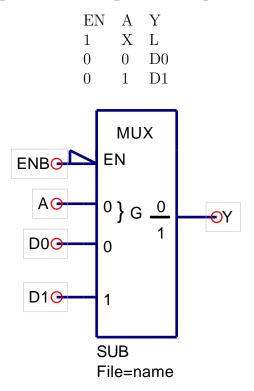

#### MUX4to1 - 4 input to 1 multiplexer

| А | EN               | Y                        |

|---|------------------|--------------------------|

| Х | 1                | 0                        |

| 0 | 0                | D0                       |

| 1 | 0                | D1                       |

| 0 | 0                | D2                       |

| 1 | 0                | D3                       |

|   | X<br>0<br>1<br>0 | X 1<br>0 0<br>1 0<br>0 0 |

2 bit adder

#### Subcircuit VHDL code generated by Ques

Ques generates a separate entity-architecture model for each subcircuit. These component definitions are compiled into the work library by FreeHDL. Here is the VHDL code from two of the previous examples.

#### Gen2bit

```

entity Sub_gen2bit is

port (CLK: in bit;

R: in bit;

nnout_B0: out bit;

nnout_B1: out bit );

end entity;

use work.all;

architecture Arch_Sub_gen2bit of Sub_gen2bit is

signal B0b,

B1b,

JK,

nnnet0,

B0,

B1 : bit;

begin

FF0 : process (nnnet0, R, CLK)

begin

if (R='1') then B0 <= '0';

elsif (nnnet0='1') then B0 <= '1';

elsif (CLK='1' and CLK'event) then

B0 \ll (JK \text{ and not } B0) \text{ or } (not JK \text{ and } B0);

end if;

end process;

B0b \leq not B0;

FF1 : process (nnnet0, R, B0b)

begin

if (R='1') then B1 <= '0';

elsif (nnnet0='1') then B1 <= '1';

elsif (B0b='1' and B0b'event) then

B1 \ll (JK \text{ and not } B1) \text{ or } (not JK \text{ and } B1);

end if;

end process;

B1b \leq not B1;

SUB2: entity Sub_logic_zero port map (nnnet0);

nnout_B0 \leq B0 or '0':

nnout_B1 \le B1 \text{ or } '0';

SUB1: entity Sub_Logic_one port map (JK);

end architecture;

```

#### 2 bit adder

entity Sub\_fadd\_2bit is

```

port (A1: in bit;

B1: in bit;

A2: in bit;

B2: in bit;

CI: in bit;

nnout_S1: out bit;

nnout_S2: out bit;

nnout_CO: out bit );

end entity;

use work.all;

architecture Arch_Sub_fadd_2bit of Sub_fadd_2bit is

signal nnnet0,

nnnet1,

nnnet2,

nnnet3,

nnnet4,

nnnet5,

nnnet6,

S2,

CO,

S1 : bit;

begin

S1 \ll CI \text{ xor } B1 \text{ xor } A1;

nnnet0 \leq B2 xor A2;

nnnet1 \leq nnnet0 and nnnet2;

nnnet3 \leq B2 and A2;

nnnet2 \leq nnnet4 or nnnet5;

nnnet4 <= nnnet6 and CI;

nnnet5 \leq B1 and A1;

S2 \ll B2 \text{ xor } A2 \text{ xor } nnnet2;

CO \ll nnnet3 or nnnet1;

nnnet6 \leq B1 xor A1;

nnout_S2 \leq S2 or '0';

nnout_CO <= CO or '0';

nnout_S1 <= S1 or '0';

end architecture;

```

#### Notes on subcircuit VHDL generation

- Ques predefined digital components generate concurrent data flow signal statements or process statements.

- Previously defined subcircuit symbols generate VHDL port map statements.

- Type out entity port signals are prevented from being read as input signals by masking each output signal using the logic function **signal-name OR** '0'.<sup>8</sup>

- A VHDL

use work.all;

statement is included before each subcircuit architecture definition to ensure that FreeHDL can find any nested subcircuits <sup>9</sup>.

• The complete VHDL code file for a digital design is composed from an outer test bench entity-architecture model plus entity-architecture models for each subcircuit specified in the design,

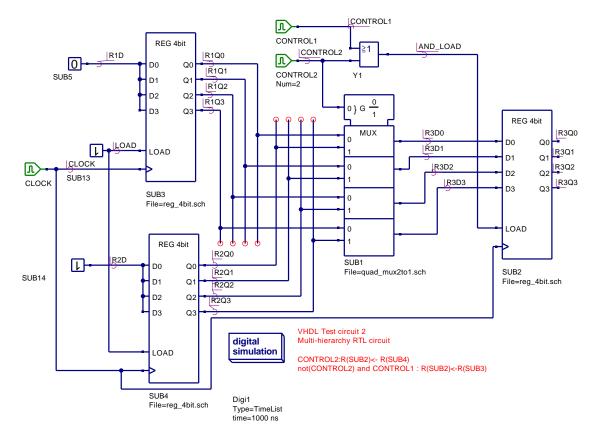

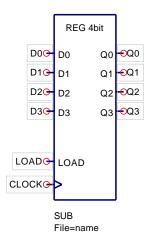

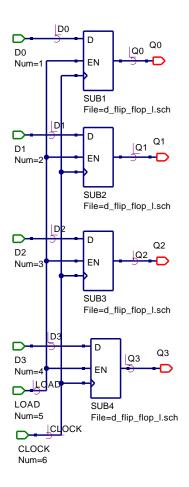

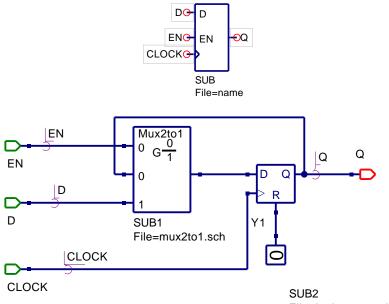

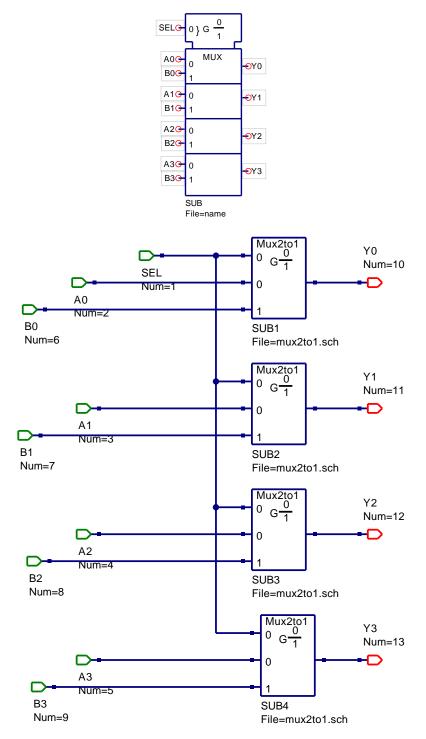

## Subcircuit nesting: A more complex design example

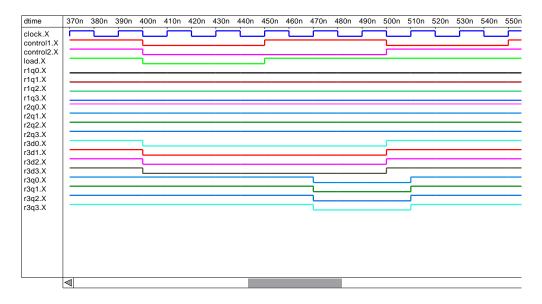

In theory there is no limit to the depth of subcircuit nesting allowed by Ques. In practice most digital circuit schematics can be constructed with a maximum of four or five levels of design hierarchy. Figure 8 shows an example that was used to test Ques subcircuit nesting performance. The design is a simple RTL function that uses a multiplexer to transfer data from one of two input registers to a single output register. The next section of these notes outlines in detail the specification of the subcircuits needed to build the RTL design. A set of sample simulation waveforms showing the register transfer operation are illustrated in Fig. 9.

<sup>&</sup>lt;sup>8</sup>Attempting to read entity port signals of type out results in a VHDL compile error.

<sup>&</sup>lt;sup>9</sup>Strictly speaking it should not be necessary to specifically state the use of the work library as this library is normally visible at all times when compiling entity-architecture models. However, at this stage in the development of FreeHDL it does appear that it is necessary when using the default FreeHDL VHDL library mapping.

#### 4 bit RTL design

Figure 8: Top level schematic.

Reg4bit

#### D flip-flop with load enable

File=logic\_zero.sch

Mux2to1

#### QuadMux

Figure 9: Sample simulation waveforms for RTL design.

#### Update number one: May 2006

Although it is only a short time since the first version of these digital tutorial notes was posted on the Ques Sourceforge Web site, much has happened in the world of Ques digital simulation. Bugs in the Ques code have been found, and fixed, and a range of new features added to the software. These expand the power of Ques digital simulation and give users a glimpse of how the package will evolve in the future. The purpose of these notes is firstly to update readers as to the changes to Ques digital simulation and secondly to explain how to use the new Ques features. Please note however, they are not intended to teach readers how to program using VHDL.<sup>10</sup>

#### Bugs, corrections and small changes to the Qucs digital simulation code

All the bugs reported in the first version of these notes have been corrected in the latest Ques CVS code. These corrections are, of course, also included in Ques release 0.0.9. During testing a number of other annoying, but significant, bugs have also been found and eliminated, these include

<sup>&</sup>lt;sup>10</sup>A good introduction to the VHDL language and it's application in digital system design can be found in *Digital System Design using VHDL* by Charles H. Roth, Jr, PWS Publishing Company, 1997, ISBN 0-534-95099-X.

- Multiple input gates (three or more inputs) of types nand and nor failed at the FreeHDL compile stage due to an error in the VHDL code generated by Ques.

- Signals names and, for example, component names constructed from a single letter that was an abbreviation for a physical unit failed to compile.

- Changing digital component time delays caused component connections on a schematic to be removed.

- GUI problems caused by errors in the symbol rotation and mirror code.

- Quesconv code conversion errors caused the Ques digital simulation cycle to fail before plotting TimeList waveforms.

A number of changes to either the VHDL code generated by Qucs or the schematic capture GUI have been introduced, these include

• The VHDL code generated by Qucs for the ground symbol has been changed from

gnd <= gnd and '0'; to gnd <= '0';</pre>

• The symbol for digital inout ports has been changed from the analogue pin symbol to one that consists of the digital in and out pins drawn back-to-back. This reflects the bidirectional status of an inout port.

A more complete list of all the bug corrections and other program modifications can be found in the Ques change log files.

#### New digital simulation features

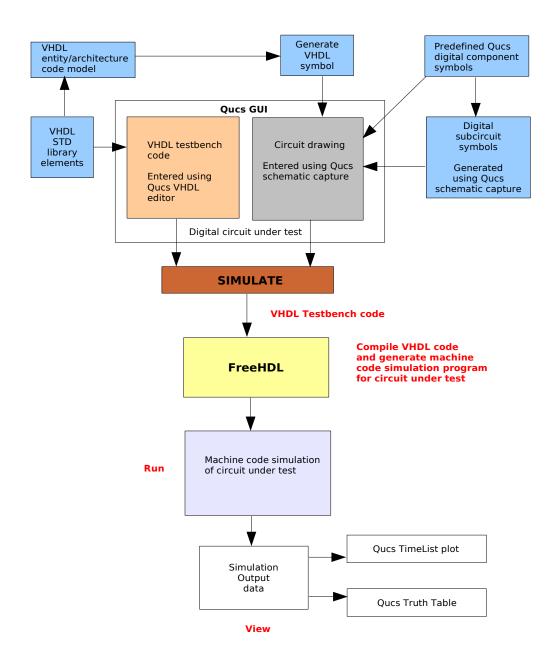

The flow diagram illustrated in Fig. 10 shows a number of different simulation routes for a digital circuit under test. The Ques digital simulation facilities have been improved to include direct simulation of VHDL testbench code and the simulation of circuit schematics that include digital components specified by VHDL entity-architecture models. The various combinations that users can adopt for Ques digital circuit entry are as follows:

- 1. Schematic circuit entry using predefined digital component symbols, subcircuits generated using the same symbols and a copy of the digital simulation icon; this is the approach described in the first version of these tutorial notes.

- 2. Circuit entry identical to 1 plus symbols for digital components specified by VHDL entity-architecture models.

- 3. Circuit entry using the Ques VHDL code editor. The text entered describes both the circuit under test and the test vectors needed to drive the circuit inputs during simulation.

Once the circuit under test has been entered into Ques, clicking the Simulate menu button, or pressing key F2, starts the Ques digital simulation process.

#### Limitations

Before describing the new digital simulation features it is important that readers understand the limitations that are inherent in the various digital simulation routes described in the last section and illustrated in the flow diagram shown in Fig. 10. Ques schematic capture allows users to draw circuits consisting of predefined component symbols and subcircuit symbols. At this stage in the development of the GUI digital signals must be of type bit (as defined in the VHDL standard library - library STD in the FreeHDL package) where individual signals flow through a single wire. Ques schematic drawing bus structures of VHDL type bit-vector, for example, have not been implemented yet. This implies that the device symbol port pins must represent single signals. Similarly the nets connecting pins on more than one device can only be single signal nets and not bus structures. It is anticipated that this will change in a future Ques release.

Although the current release of FreeHDL is 0.0.1 the package implements a substantial subset of the entire VHDL language<sup>11</sup>. The major features not supported by release 0.0.1 are:

- Shared variables.

- The following attributes; transaction, quiet, stable and delayed.

- User defined attributes.

- Groups.

<sup>&</sup>lt;sup>11</sup>A complete description of the 1987 and 1993 specifications of the VHDL language can be found in The Designer's Guide to VHDL by Peter J Ashenden, second edition 2002, Morgan Kaufmann Publishers, ISBN 1-55860-674-2.

Figure 10: Flow diagram of Ques digital simulation routes.

- Guarded signal assignments.

- Currently drivers cannot be switched off.

The Ques TimeList plotting program uses signal data output by the machine code simulation program generated by the FreeHDL package<sup>12</sup>. A current limitation of the TimeList plotting program is that it can only display signals of type bit. Bus signal waveforms cannot be displayed.

Given the above limitations it is therefore possible to write VHDL code that can be compiled by FreeHDL but will cause problems at either the schematic drawing or output waveform plotting stages in the Ques simulation cycle. As Ques develops it is expected that these limitations will be removed. On the subject of limitations one final point to note: FreeHDL can simulate circuits described by the data types and other features found in the

#### IEEE.std\_logic\_1164

library and other predefined libraries. However, at this stage in the development of the Ques software only the VHDL standard library may be used, implying that data type bit must be used to represent logic signals.

#### Using the Ques VHDL editor

Ques release 0.0.9 includes a VHDL text editor<sup>13</sup> that has all the usual edit features plus colour coding of the various VHDL language statements. One unusual feature of this editor is a zoom control that allows the text size to be increased or decreased in a similar way to the schematic drawing zoom. The VHDL editor is included in the Ques package for two primary purposes, firstly for purely text file VHDL simulation<sup>14</sup> and secondly for the development of VHDL entity-architecture models that can be linked to schematic capture symbols. The latter increases significantly the capabilities of the Ques software in that it allows libraries of hand-crafted device models to be constructed. These new library devices will, given support by the general Ques user community, greatly expand the potential use of the Ques package. In this section the use of the VHDL text editor is demonstrated through a series of digital circuit simulation examples. The included VHDL listings indicate typical Ques use of a number of the basic VHDL data types. The text also outlines any limitations imposed by Ques.

$<sup>^{12}</sup>$ The machine code simulation program outputs signal data in VCD format. This is then converted to the Ques TimeList data format by the quesconv utility program.

<sup>&</sup>lt;sup>13</sup>To launch the new VHDL editor click on the second icon from the left on the Ques toolbar. It can also be activated using the key sequence Ctrl+Shift+V.

<sup>&</sup>lt;sup>14</sup>This is still the preferred method amongst many experienced users of VHDL. However, the circuit schematic drawing approach does seem to be growing in popularity.

• Example 1: A sum of products (SOP) combinational digital circuit. The Boolean equation<sup>15</sup> for a SOP combinational circuit is:

$$f = \overline{W}.X.\overline{Y}.\overline{Z} + \overline{W}.\overline{X}.\overline{Y}.\overline{Z} + W.\overline{Y}.\overline{Z} + W.X.Y.Z$$

The VHDL code for a structural model of this combinational circuit and its associated testbench is given in the following listing.

```

-- Ques VHDL editor example 1

entity test_vector is -- Test vector generator.

port(z, y, x, w : out bit

);

end entity test_vector;

architecture behavioural of test_vector is

begin

pz : process is

begin

z \ <= \ '0'; wait for 20 ns;

z <= '1'; wait for 20 ns;

end process pz;

py : process is

begin

end process py;

px : process is

begin

x \ll '0'; wait for 80 ns;

x \le '1'; wait for 80 ns;

end process px;

pw : process is

begin

w \le '0'; wait for 160 ns;

w <= '1'; wait for 160 ns;

end process pw;

end architecture behavioural;

entity and 4 is --- 4 input and gate.

```

<sup>&</sup>lt;sup>15</sup>The Boolean equation for function f has not been minimised. It is in a form derived directly from a truth table and is introduced purely as an example to demonstrate the use of the Ques VHDL editor.

```

port(in1, in2, in3, in4 : in bit;

out1 : out bit

);

end entity and4;

architecture dataflow of and4 is

begin

out 1 \le in1 and in2 and in3 and in4;

end architecture dataflow;

entity and 3 is -- 3 input and gate.

port(in1, in2, in3 : in bit;

out1 : out bit

);

end entity and3;

architecture dataflow of and3 is

begin

out 1 \le in1 and in2 and in3;

end architecture dataflow;

entity or4 is --- 4 input or gate.

port(in1, in2, in3, in4 : in bit;

out1 : out bit

);

end entity or4;

architecture dataflow of or4 is

begin

out 1 \le in1 or in2 or in3 or in4;

end architecture dataflow;

entity inv is -- Inverter.

port( in1 : in bit;

out1 : out bit

);

end entity inv;

architecture dataflow of inv is

begin

out1 <= not in1;

end architecture dataflow;

```

```

entity testbench is

Test bench outer entity wrapper.

___

end entity testbench;

library work;

use work.all;

architecture structural of testbench is -- Testbench architecture.

signal b0, b1, b2, b3, zb, yb, xb, wb,a, b, c, d, f : bit;

begin

d1 : entity test_vector port map(b0, b1, b2, b3);

d2 : entity inv port map(b0, wb);

d3 : entity inv port map(b1, xb);

d4 : entity inv port map(b2, yb);

d5 : entity inv port map(b3, zb);

d6 : entity and 4 port map(zb, yb, b1, wb, a);

d7 : entity and4 port map(zb, yb, xb, wb, b);

d8 : entity and 3 port map(zb, yb, b0, c);

d9 : entity and 4 port map(b0, b1, b2, b3, d);

d10 : entity or 4 port map(a, b, c, d, f);

end architecture structural;

```

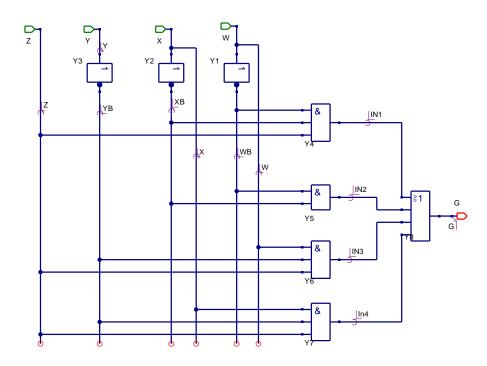

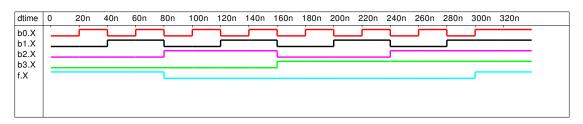

On entry of this code into the Ques VHDL text editor the text is colour coded. Unfortunately, the colour coding is lost when printed, or pasted into a word processor, or a layout package like LaTeX. The structure of the VHDL listing follows the normal convention for text based VHDL simulation. All component entity-architecture models must be defined before they are referenced in other component models. The simulation test bench must be the last entity-architecture model in the VHDL listing. During the VHDL compile phase FreeHDL compiles the component entity-architecture models to the work library<sup>16</sup>. These compiled models are then made available to the simulation test bench through the use of the VHDL use statement inserted in the listing prior to the testbench architecture statement. Once the VHDL listing for the simulation has been typed into the Ques VHDL code editor, pressing key F2 starts the simulation process. The simulation duration can be set using the Document Settings in the File dropdown menu (or by pressing the Ctrl+. keys). Any VHDL syntax errors, or indeed typos, are written to file and can be viewed by pressing key F5. Obviously if errors are reported these need to be corrected using the VHDL text editor and the simulation cycle restarted. A typical TimeList output for editor example 1 is shown in

<sup>&</sup>lt;sup>16</sup>In most VHDL implementations library work is always visible and there is no requirement to make it visible by using the library and use statements. However, FreeHDL appears to need these statements at the linking phase otherwise the VHDL compiler fails.

Figure 11: Sample simulation waveforms for VHDL editor example 1 design.

• Example 2: VHDL editor example 1 modelled using dataflow VHDL statements.

The VHDL code for the second example is given in the next listing. The VHDL style chosen to model the circuit is based on VHDL dataflow concurrent signal assignments. The input text vectors are generated using a simple state machine rather than separate process statements. The test vector generator port specification uses entirely single signal bit types and can be easily interfaced, without problems, to other components connected on a Ques schematic diagram. The procedure for generating schematic capture component symbols from entity - architecture models is introduced in a later section of these notes. The use of bit vector bus constructions is also illustrated in this example. Ques allows the use of bit vectors as signals or variables in VHDL models provided all signals in the port statement of entity declaration are of type bit only.<sup>17</sup> A typical TimeList output for editor example 2 is shown in Fig. 12.

```

-- Ques VHDL editor example 2

--

entity test_vector_a is

port( RESET, CLOCK : in bit;

B0, B1, B2, B3 : out bit

);

end entity test_vector_a;

--

architecture behavioural of test_vector_a is

signal present_state, next_state : bit_vector(3 downto 0):="1111";

begin

```

<sup>&</sup>lt;sup>17</sup>This is a restriction of Qucs 0.0.9 and will be removed in a later release of the package. Also note signals of type bit vector that are declared in architecture definitions are listed in the TimeList plot signal dialogue. However, a text message saying no data results if an attempt is made to display them. Again this limitation will be removed in a later release of Qucs.

```

p1 : process(CLOCK ) is

begin

if

(CLOCK' event and CLOCK='1') then

present_state <= next_state;</pre>

end if;

end process p1;

p2 : process(RESET, present_state) is

begin

if (RESET = '1') then next_state \leq "1111";

end if;

case present_state is

when "0000" =>

next_state \leq "0001";

when "0001"

\Rightarrow

next_state \leq "0010";

when "0010"

next_state \leq "0011";

\Rightarrow

when "0011"

next_state \leq "0100";

\Rightarrow

when "0100"

\Rightarrow next_state <= "0101";

when "0101"

next_state \leq "0110";

\Rightarrow

when "0110"

\Rightarrow

next_state \ll "0111";

next_state \leq "1000";

when "0111"

\Rightarrow

when "1000"

next_state \leq "1001";

\Rightarrow

when "1001"

\implies next_state <= "1010";

when "1010"

next_state <= "1011":

=>

when "1011"

next_state \leq "1100";

\Rightarrow

next_state \leq "1101";

when "1100"

\Rightarrow

when "1101"

next_state \leq "1110";

\Rightarrow

when "1110"

next_state \leq "1111";

\Rightarrow

next_state \leq "0000";

when "1111"

\Rightarrow

end case;

B3 \ll next_state(3); B2 \ll next_state(2);

B1 \ll next_state(1); B0 \ll next_state(0);

end process p2;

end architecture behavioural;

library work;

use work.all;

entity testbench is

end entity testbench;

architecture dataflow of testbench is

signal reset, clk, b0, b1, b2, b3, zb : bit;

```

```

signal

yb, xb, wb, a, b, c, d, f: bit;

begin

p1 : process is

begin

clk \ll '0'; wait for 10 ns;

clk <= '1'; wait for 10 ns;

end process p1;

p2 : process is

begin

reset \langle = '1'; wait for 10 ns;

reset <= '0'; wait for 2000 ns;

end process p2;

d1 : entity test_vector_a port map(reset, clk, b0, b1, b2, b3);

Data flow model of combinational circuit

wb \leq not b0; xb \leq not b1; yb \leq not b2; zb \leq not b3;

a \ll (wb \text{ and } b1) \text{ and } (yb \text{ and } zb);

b \le (wb \text{ and } xb) \text{ and } (yb \text{ and } zb);

c \ll b0 and (yb and zb);

d \leq (b0 \text{ and } b1) \text{ and } (b2 \text{ and } b3);

f \ll a \text{ or } b \text{ or } c \text{ or } d;

end architecture dataflow;

10n

20n

40n

50n

100n 110n 120n 130n 140n 150n 160n 170n

0

30n

60n

70n

80n

90n

```

Figure 12: Sample simulation waveforms for VHDL editor example 2 design.

• Example 3: VHDL editor example 1 modelled using VHDL process statements and variables.

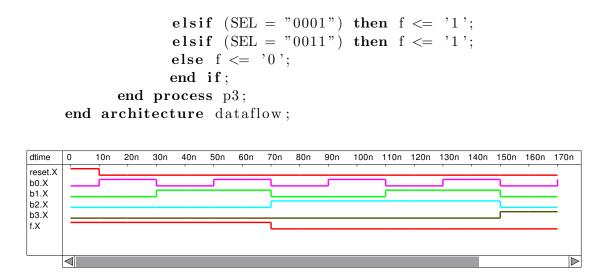

The VHDL code for the third example is given in the listing at the end of this paragraph. In this example the use of VHDL variables is illustrated. The VHDL code for the vector generator is a little unusual in that rather than using the traditional two process design employing signals, a single process statement employing variables undertakes both the calculation of the next state data and the transfer of the next state information to the present state. This approach is necessary because FreeHDL does not allowed shared variables. Once again in this example only single bit data is passed via the entity statement to the device under test. The device under test is represented by a truth table encoded in a process statement. This is not the most elegant code but it does serve the purpose of demonstrating the use of different VHDL constructions and data types in Ques digital simulation. A typical TimeList plot for VHDL editor example 3 is shown in Fig. 13. Comparison of the three output plots for the VHDL editor examples indicates that all the simulation results are very similar with some slight differences in the start up phase following the RESET pulse changing from logic '1' to logic '0'. This is probably an effect due to the different initialisation sequences for each of the test vector models.

```

-- Ques VHDL editor example 3

entity test_vector_b is

port(RESET, CLOCK : in bit;

B0, B1, B2, B3 : out

bit

):

end entity test_vector_b;

architecture behavioural of test_vector_b is

begin

p1 : process(RESET,

CLOCK) is

variable present_state , next_state :

bit_vector(3 \text{ downto } 0) := "0000";

begin

if (RESET = '1') then next_state := "0000";

elsif (CLOCK' event and CLOCK='1') then

present_state := next_state;

case present_state is

when "0000"

next_state := "0001";

=>

when "0001"

next_state := "0010";

\Rightarrow

when "0010"

next_state := "0011":

\Rightarrow

when "0011"

next_state := "0100";

=>

when "0100"

next_state :=

"0101"

=>

when "0101"

=>

next_state := "0110";

when "0110"

next_state := "0111";

\Rightarrow

when "0111"

next_state := "1000";

=>

when "1000"

next_state := "1001";

=>

when "1001"

=>

next_state := "1010";

when "1010"

=>

next_state := "1011";

```

```

when "1011"

\implies next_state := "1100";

next_state := "1101";

when "1100"

=>

when "1101"

next_state := "1110";

=>

when "1110"

=>

next_state := "1111";

when "1111"

=>

next_state := "0000";

end case;

end if;

B3 \ll next_state(3); B2 \ll next_state(2);

B1 \ll next_state(1); B0 \ll next_state(0);

end process p1;

end architecture behavioural;

library work;

use work.all;

___

entity testbench is

end entity testbench;

architecture dataflow of testbench is

signal reset, clk, b0, b1, b2, b3, f: bit;

begin

p1 : process is

begin

clk <= '0'; wait for 10 ns;

clk <= '1'; wait for 10 ns;

end process p1;

p2 : process is

begin

reset \langle = '1'; wait for 10 ns;

reset <= '0'; wait for 2000 ns;

end process p2;

d1 : entity test_vector_b port map(reset, clk, b0, b1, b2, b3);

Behavioural model of combinational circuit

p3: process(b3, b2, b1, b0) is

variable SEL : bit_vector (3 downto 0);

begin

SEL := b3\&b2\&b1\&b0 ;

if (SEL = "0010") then f \le '1';

elsif (SEL = "0000") then f <= '1';

elsif (SEL = "1111") then f <= '1';

```

Figure 13: Sample simulation waveforms for VHDL editor example 3 design.

## Linking VHDL entity-architecture models to Ques schematic device symbols

VHDL was originally developed as a hardware description language for specifying digital systems. Indeed many engineers still prefer to describe digital systems entirely in VHDL statements rather than use schematic drawings. Once written VHDL code is saved as a text file and becomes the input data for a VHDL compiler/simulation package. Through popular demand a number of digital synthesis/simulator CAD tools<sup>18</sup> have started to include a facility that links VHDL model code to a schematic capture symbol. It is then, of course, possible to use a schematic diagram as the main entry media<sup>19</sup> when designing and simulating a digital design. Ques release 0.0.9 has such a facility, allowing VHDL code models to be linked to schematic symbols. When drawing digital design schematics, these user defined symbols may be mixed with the Ques predefined digital symbols and other user defined subcircuit symbols. The process for linking VHDL code to Ques schematic drawing symbols is straightforward and will be illustrated in these notes through two examples.

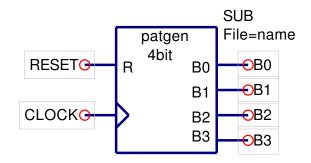

• Example 4: A 4 bit test vector pattern generator.

<sup>&</sup>lt;sup>18</sup>See for example the XILINX, WebPACK software at http//www.xilinx.com/ise/logic\_design\_prod/webpack.htm.

<sup>&</sup>lt;sup>19</sup>Please note that at the start of the VHDL simulation process schematic drawings are converted into a VHDL text file.

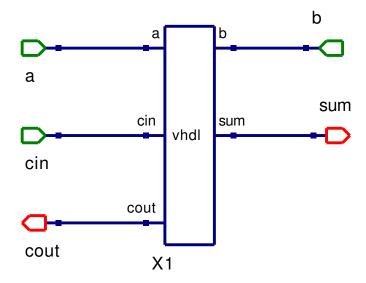

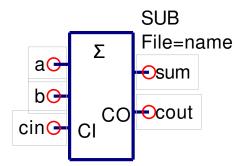

Shown in Table 4 is the VHDL entity-architecture model listing for a 4 bit binary pattern generator. The VHDL code is identical to the test vector code introduced in the third VHDL editor example. After entering the VHDL entity-architecture model code using the Ques VHDL editor the finished text is saved in a file with a suitable name and file extension vhdl. Ques then lists the model under the VHDL project category. Simply clicking on a model name in the VHDL category, with the left hand mouse button, then moving the mouse pointer to a suitable position on a schematic, causes Ques to move a symbol that represents the model onto the schematic drawing sheet. Placement of the symbol at the position located by the mouse pointer is achieved by clicking the left hand mouse button. The procedure is identical to that used to select and place the Ques predefined symbols on a schematic drawing. Ques automatically generates a rectangular symbol with a name called VHDL that has the same number of pins as the port statement listed in the VHDL model entity statement. Each of the pins is given a name that corresponds to a name in the entity statement. Ques fixes the order of the pins on the generated symbol. It appears that it is not possible to edit this symbol. However, subcircuit in, out or inout port symbols can be attached to symbol VHDL and a user edited symbol generated. Fig. 14 shows the Ques generated VHDL symbol with attached ports for the model listed in Table 4. The edited symbol for the 4 bit binary pattern generator is illustrated in Fig. 15. Notice that in Fig. 15 the order of the pins has been changed to reflect the natural order for a device with it's input pins on the left and output pins on the right. VHDL model symbols can also be generated by placing the VHDL file component, this is located in the digital components viewlist, on a schematic. On editing the VHDL file name property of this device to the name of a VHDL entity-architecture model file, Ques automatically generates a VHDL symbol. Defining your own symbol then proceeds in a similar fashion to the way described above.

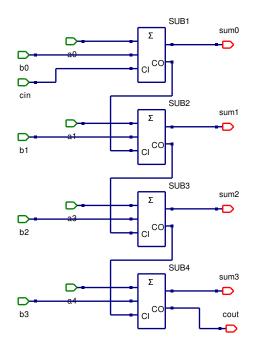

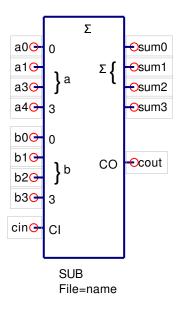

• Example 5: A 4 bit full adder.

VHDL model symbols may be combined with either the Ques predefined digital component symbols or other subcircuit symbols. In this example a VHDL model for a simple one bit full adder is connected four times in a serial fashion to form a 4 bit full adder. The VHDL model code for a simple one bit full adder is given in Table 5. The associated symbol diagrams for the one bit full adder are illustrated in Fig. 16 and Fig. 17.

```

entity patgen_4bit is

port( RESET, CLOCK : in bit;

B0, B1, B2, B3 : out

bit

):

end entity patgen_4bit;

architecture behavioural of patgen_4bit is

begin

p1 : process(RESET, CLOCK) is

variable present_state , next_state :

bit_vector(3 \text{ downto } 0) := "0000";

begin

if (RESET = '1') then next_state := "0000";

elsif (CLOCK'event and CLOCK='1') then

present_state := next_state;

case present_state is

when "0000"

=>

next_state := "0001";

when "0001"

=>

next_state := "0010";

when "0010"

next_state := "0011"

=>

when "0011"

next_state := "0100";

=>

when "0100"

next_state := "0101";

\Rightarrow

when "0101"

next_state := "0110";

\Rightarrow

when "0110"

=>

next_state := "0111";

when "0111"

next_state := "1000";

=>

when "1000"

\implies next_state := "1001";

when "1001"

next_state := "1010";

=>

when "1010"

next_state := "1011";

=>

when "1011"

next_state := "1100":

=>

when "1100"

next_state := "1101";

=>

when "1101"

\implies next_state := "1110";

when "1110"

\Rightarrow

next_state := "1111";

when "1111"

=>

next_state := "0000";

end case:

end if;

B3 \ll next_state(3); B2 \ll next_state(2);

B1 \ll next_state(1); B0 \ll next_state(0);

end process p1;

end architecture behavioural;

```

Table 4: VHDL code for a 4 bit pattern generator.

Figure 14: Ques generated VHDL symbol with subcircuit ports for test pattern generator.

Figure 15: User defined 4 bit pattern generator symbol.

```

-- Full adder - 1 bit

entity fulladder is

port (a, b, cin : in bit;

sum, cout : out bit

);

end entity fulladder;

---

architecture dataflow of fulladder is

begin

sum <= (a xor b) xor cin;

cout <= (a and b) or (a and cin) or (b and cin);

end architecture dataflow;</pre>

```

Table 5: VHDL code for a 1 bit full adder.

Figure 16: Ques generated VHDL symbol with subcircuit ports for one bit full adder.

Figure 17: User defined one bit full symbol.

Figure 18 shows the schematic for a simple 4 bit ripple adder. The corresponding user defined symbol for the 4 bit full adder is given in Fig. 19.

Figure 18: 4 bit full adder schematic.

#### Generating VHDL code from Ques schematic drawings

Pressing key F2 causes Ques to simulate the design entered by the Ques user. The input data for a simulation is either a VHDL text file, saved from the VHDL text editor, or a VHDL code file generated by Ques using the information encoded on a schematic drawing. In this section of these tutorial notes a larger design is introduced and the resulting VHDL code and simulation results are discussed.

Figure 19: User defined 4 bit full adder symbol.

|    |      |      |      | b3   | b2   | b1   | b0   |

|----|------|------|------|------|------|------|------|

|    |      |      |      | a3   | a2   | a1   | a0   |

|    |      |      |      | a0b3 | a0b2 | a0b1 | a0b0 |

|    |      |      | a1b3 | a1b2 | a1b1 | a1b0 |      |

|    |      | a2b3 | a2b2 | a2b1 | a2b0 |      |      |

|    | a3b3 | a3b2 | a3b1 | a3b0 |      |      |      |

| r7 | r6   | r5   | r4   | r3   | r2   | r1   | r0   |

|    |      |      |      |      |      |      |      |

Table 6: Product table for a 4 bit by 4 bit combinational multiplier.

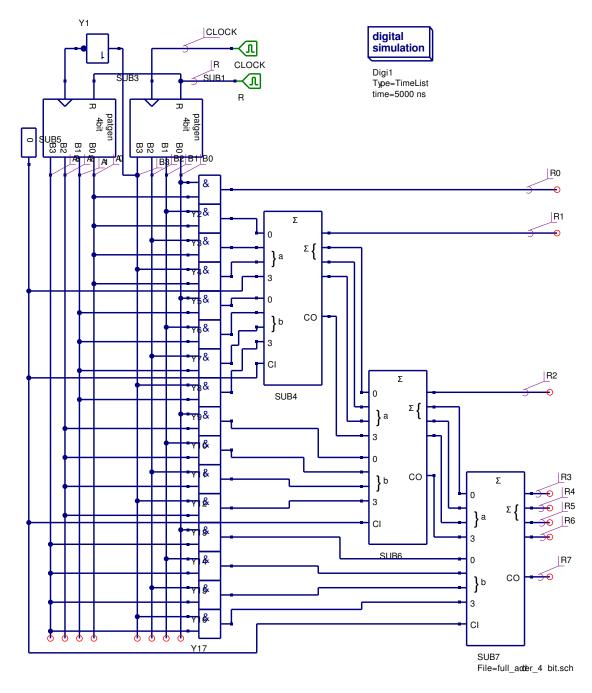

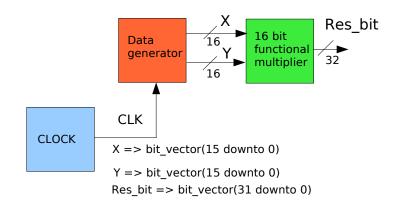

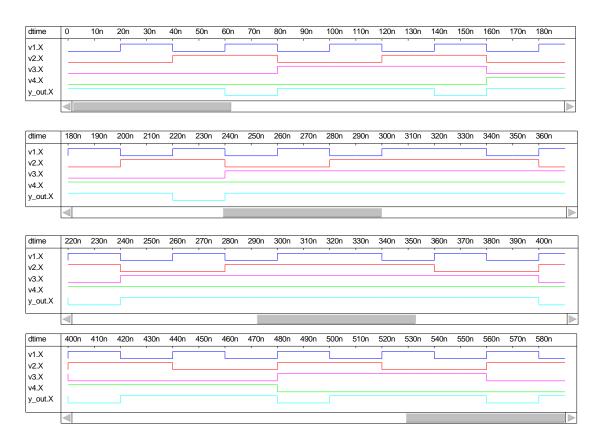

The example chosen for this purpose is a 4 bit by 4 bit combinational digital multiplier. Both the 4 bit pattern generator and the 4 bit full adder outlined in the last section form part of the central core of the 4 bit multiplier design and it's associated testbench. Table 6 shows the multiplication product table for a 4 bit by 4 bit combinational binary multiplier. Inputs to the device are binary bits a3 a2 a1 a0 and b3 b2 b1 b0. The 4 by 4 multiplier device requires 16 and gates (to generate the multiplier product terms), three four bit full adders (to sum the output r terms) and two 4 bit pattern generators to test the 256 possible input states. The multiplier output is represented in Table 6 by r7 r6 r5 r4 r3 r2 r1 and r0. The circuit schematic for the 4 bit by 4 bit multiplier and test bench are given in Fig. 20.

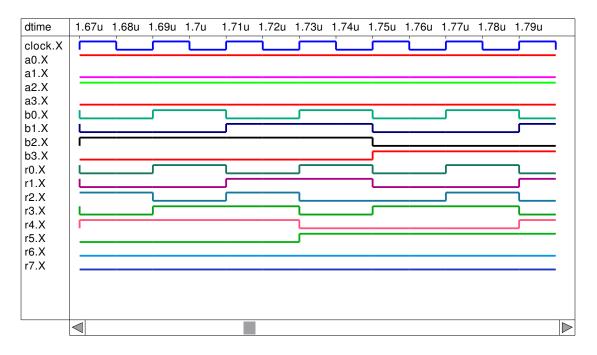

The VHDL code for this example is presented in the following listing. This listing

was generated by Qucs<sup>20</sup>. A small section of the TimeList waveform plot for the digital multiplier is shown in Fig. 21. At 1.74 micro seconds input a is "0101", input b is "0111" and the output r is "00100011" which is 35 in decimal. Taking a few random checks of the simulation results indicates that the 4 bit by 4 bit multiplier design works correctly. Notice that the VHDL code generated by Qucs for the 4 bit multiplier does not contain any propagation delay timing data. This could be added to the and gates, if required. However, at this stage in the development of Qucs digital simulation passing timing data, and other parameters, from device symbols generated from VHDL models has not been implemented yet. The use of VHDL generics is an obvious way this could be done. Generics are allowed, of course, in text based VHDL simulations.

<sup>&</sup>lt;sup>20</sup>Some readers will have noticed that the naming scheme for internal signal nets is different in the multiplier VHDL listing when compared to the VHDL listings in the first version of these notes. Towards the end of the 0.0.9 development phase the naming convention employed by Ques was changed to give a more flexible structure.

Figure 20: A 4 bit by 4 bit combinational digital multiplier.

```

-- Ques 0.0.9

- /mnt/hda2/vhdl_comp_lib_prj/multiplier_4bx4bit.sch

entity patgen_4bit is

port(RESET, CLOCK : in bit;

B0, B1, B2, B3 : out

bit

);

end entity patgen_4bit;

architecture behavioural of patgen_4bit is

begin

p1 : process(RESET, CLOCK) is

variable present_state , next_state :

bit_vector(3 \text{ downto } 0) := "0000";

begin

if (RESET = '1') then next_state := "0000";

elsif (CLOCK'event and CLOCK='1') then

present_state := next_state;

case present_state is

when "0000" \implies next_state := "0001";

when "0001"

\implies next_state := "0010";

when "0010"

\implies next_state := "0011";

when "0011"

\implies next_state := "0100";

when "0100"

next_state := "0101":

=>

when "0101"

\implies next_state := "0110";

when "0110"

\Rightarrow next_state := "0111";

when "0111"

\implies next_state := "1000";

when "1000"

\implies next_state := "1001";

when "1001"

\Rightarrow next_state := "1010";

when "1010"

\implies next_state := "1011";

when "1011"

\implies next_state := "1100";

when "1100"

\implies next_state := "1101";

when "1101"

\implies next_state := "1110";

when "1110"

\implies next_state := "1111";

when "1111"

\implies next_state := "0000";

end case;

end if:

B3 \ll next_state(3); B2 \ll next_state(2);

B1 \ll next_state(1); B0 \ll next_state(0);

end process p1;

end architecture behavioural;

```

```

entity Sub_patgen_4bit is

```

```

port (net_net0: in bit;

net_net5: in bit;

net_outnet_net1: out bit;

net_outnet_net3: out bit;

net_outnet_net2: out bit;

net_outnet_net4: out bit );

end entity;

use work.all;

architecture Arch_Sub_patgen_4bit of Sub_patgen_4bit is

signal net_net1,

net_net2,

net_net3,

net_net4 : bit;

begin

net_outnet_net1 <= net_net1 or '0';</pre>

net_outnet_net2 \ll net_net2 or '0';

net_outnet_net3 <= net_net3 or '0';</pre>

net_outnet_net4 <= net_net4 or '0';</pre>

X1: entity patgen_4bit port map (net_net0, net_net5,

net_net1 , net_net3 , net_net2 , net_net4 );

end architecture;

logic_zero.vhdl

___

entity logic_zero is

port(Y: out bit

);

end entity logic_zero;

architecture dataflow of logic_zero is

begin

Y <= '0';

end architecture dataflow;

entity Sub_logic_zero is

port (net_outnetY: out bit);

end entity;

use work.all;

architecture Arch_Sub_logic_zero of Sub_logic_zero is

signal netY : bit;

begin

X1: entity logic_zero port map (netY);

```

```

net_outnetY \leq netY \text{ or } '0';

end architecture;

Full adder - 1 bit

entity fulladder is

port (a, b, cin : in bit;

sum, cout : out bit

):

end entity fulladder;

architecture dataflow of fulladder is

begin

sum \ll (a xor b) xor cin;

cout \ll (a and b) or (a and cin) or (b and cin);

end architecture dataflow;

entity Sub_full_adder_1bit is

port (net_net0: in bit;

net_net1: in bit;

net_net2: in bit;

net_outnet_net3: out bit;

net_outnet_net4: out bit);

end entity;

use work.all;

architecture Arch_Sub_full_adder_1bit of Sub_full_adder_1bit is

signal net_net3,

net_net4 : bit;

begin

X1: entity fulladder port map (net_net0, net_net1,

net_net2 , net_net3 , net_net4 );

net_outnet_net3 <= net_net3 or '0';</pre>

net_outnet_net4 <= net_net4 or '0';</pre>

end architecture;

entity Sub_full_adder_4bit is

port (net_net0: in bit;

net_net1: in bit;

net_net2: in bit;

net_net3: in bit;

net_net4: in bit;

```

```

net_net5: in bit;

net_net6: in bit;

net_net13: in bit;

net_net7: in bit;

net_outnet_net8: out bit;

net_outnet_net9: out bit;

net_outnet_net10: out bit;

net_outnet_net11: out bit;

net_outnet_net12: out bit);

end entity;

use work.all;

architecture Arch_Sub_full_adder_4bit of Sub_full_adder_4bit is

signal net_net14,

net_net15,

net_net16,

net_net8,

net_net9,

net_net10,

net_net11,

net_net12 : bit;

begin

net_outnet_net8 <= net_net8 or '0';</pre>

net_outnet_net9 <= net_net9 or '0';</pre>

net_outnet_net10 \ll net_net10 or '0';

net_outnet_net11 \leq net_net11  or '0';

net_outnet_net12 \ll net_net12 or '0';

SUB4: entity Sub_full_adder_1bit port map (net_net3, net_net13,

net_net14 , net_net11 , net_net12 );

SUB3: entity Sub_full_adder_1bit port map (net_net2, net_net6,

net_net15 , net_net10 , net_net14 );

SUB2: entity Sub_full_adder_1bit port map (net_net1, net_net5,

net_net16 , net_net9 , net_net15 );

SUB1: entity Sub_full_adder_1bit port map (net_net0, net_net4,

net_net7 , net_net8 , net_net16 );

end architecture;

entity TestBench is

end entity;

use work.all;

architecture Arch_TestBench of TestBench is

signal netA0, netA1, netA2, netA3, netR, netB0,

netB1, netB2, netB3, netR0, netR1, netR2,

```

```

netR3, netR4, netR5, netR6, netR7, netCLOCK,

net_net0, net_net1, net_net2, net_net3, net_net4,

net_net5, net_net6, net_net7, net_net8, net_net9,

net_net10, net_net11, net_net12, net_net13, net_net14,

net_net15, net_net16, net_net17, net_net18, net_net19,

net_net20, net_net21, net_net22, net_net23,

net_net24 : bit;

begin

SUB3: entity Sub_patgen_4bit port map (netR, net_net0,

netA0, netA1, netA2, netA3);

SUB1: entity Sub_patgen_4bit port map (netR, netCLOCK,

netB0, netB1, netB2, netB3);

R: process

begin

netR <= '1';

wait for 10 ns;

netR <= '0';

wait for 2000 ns;

end process;

CLOCK: process

begin

netCLOCK \le '0'; wait for 10 ns;

netCLOCK <= '1'; wait for 10 ns;

end process;

net_net0 \ll not netB3;

netR0 \ll netA0 and netB0;

net_net1 \ll netA0 and netB1;

net_net2 \ll netA0 and netB2;

net_net3 \ll netA0 and netB3;

SUB5: entity Sub_logic_zero port map (net_net4);

net_net5 \le netA1 and netB0;

net_net6 \ll netA1 and netB1;

net_net7 \ll netA1 and netB2;

net_net8 \ll netA1 and netB3;

net_net9 \ll netA2 and netB0;

net_net10 \le netA2 and netB1;

net_net11 \ll netA2 and netB2;

net_net12 \ll netA2 and netB3;

SUB4: entity Sub_full_adder_4bit port map (net_net1, net_net2,

net_net3, net_net4, net_net5, net_net6, net_net7,

net_net8, net_net4, netR1, net_net13, net_net14,

```

end architecture;

Figure 21: A section of the 4 bit by 4 bit combinational digital multiplier TimeList output waveforms.

# Update number two: September 2006

Update number two in this tutorial series reports on the major changes that have taken place to Ques digital simulation since the first update was posted on the Ques

Web site roughly three months ago. During this period a number of significant, and very critical, extensions have been implemented. Previous releases concentrated on establishing a fundamental base for digital circuit simulation using the VHDL language. The primary vehicle for representing circuit signals being the VHDL bit and bit-vector signal types. The next release of Qucs (version 0.0.10) and FreeHDL (version 0.0.3) extends the allowed signal types to include IEEE std\_logic\_1164 nine level logic, integers, and reals. Readers will appreciate that these changes are the result of a great deal of work by the Ques team and must be considered as very much work in progress because not all the features offered by the FreeHDL implementation of the VHDL language are currently available via the Ques schematic capture and VHDL text file simulation routes. Although a significant amount of testing has taken place it is likely that software bugs will come to light as more Ques users try the new features - if you find a bug please report it by posting a note on the Ques Web site. Adding new signal types to Ques digital simulation affects all sections of the simulation route from schematic capture to plotting and tabulating input and output signals. Hence, although it may seem the wrong way round, the place to first implement the necessary changes to accommodate the new signal types is at the simulation results reporting stages of the Ques package. In release 0.0.10 no attempt has been made to add the new signal types to the schematic capture part of the Ques package.<sup>21</sup> Recent work on the digital sections of the Ques package has concentrated on (1) improvements to VHDL language entry using the Ques colour coded VHDL text  $editor^{22}$ , (2) modifications to Free-HDL which allow a cleaner interface between Ques and FreeHDL, (3) upgrades to the data conversion of simulation results from the FreeHDL value change dump format to the native Ques format, and (4) major changes to the results reporting routines that are accessed from the Ques diagrams icon dialogue. A detailed list of the software changes and bug fixes can be found in the Ques and FreeHDL change log files.

#### Simulating VHDL code using Ques and FreeHDL.

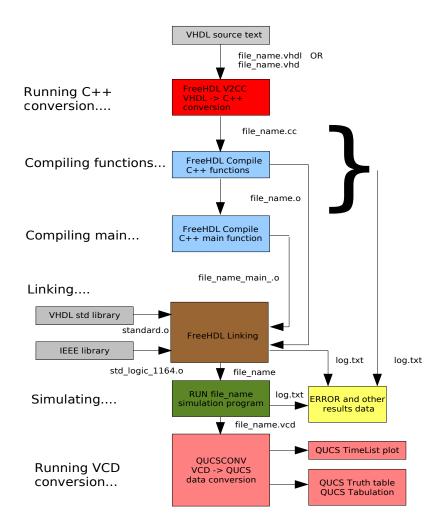

The flow diagram drawn in Fig. 10 shows the relationship between Qucs and Free-HDL, and the sequence that takes place during digital circuit simulation. This flow diagram does not however, outline the details of the stages that are performed when converting (1) VHDL circuit code into a machine code simulation program, and (2) simulation output results into a format that can be plotted and tabulated by Qucs. These are illustrated in the flow diagram presented in Fig. 22. The shell script qucsdigi controls each of the stages in this sequence. A basic understanding

<sup>&</sup>lt;sup>21</sup>Adding new signal types to Ques schematic capture is on the to-do list.

$<sup>^{22}</sup>$ A number of editor bugs have been fixed and it is now possible for users to define their own colour scheme for the various classes of VHDL reserved words and data types.

of the process employed by Ques and FreeHDL is needed if users of the software are to be able to write meaningful VHDL code and simulate it using the two packages. VHDL code is either generated from a schematic diagram automatically by Ques or entered using the Ques VHDL text editor. The use of the schematic entry route was described in update one of these tutorial notes. However, a number of readers will probably have spotted that included in the VHDL code generated by Ques are references to VHDL libraries. The VHDL language uses libraries to provide features that are not specified in the basic language definition but are commonly used by all language processing systems; two such libraries are STD and IEEE. When simulating digital circuits a basic knowledge of the structure of a simulation task and how these employ VHDL libraries is essential. This implies that users of the Qucs/FreeHDL software must appreciate how the system compiles and simulates a VHDL circuit simulation task. Once the VHDL simulation code has been entered via the VHDL text editor clicking the Ques simulation button runs shell script quesdigi performing the sequence shown in Fig.  $22^{23}$ . Program freeehdl-v2cc converts VHDL code into C++ functions. These are then compiled along with a main C++ function. The next stage in the sequence links the compiled object code with the object code from any references to items in the predefined VHDL libraries to produce an executable digital simulation program. This is then run by Ques outputting a set of simulation results in value change dump (VCD) format<sup>24</sup>. Finally a program called quesconv converts the VCD simulation results into the Ques native data format ready for post processing as graphical or tabular diagrams by Qucs.

<sup>&</sup>lt;sup>23</sup>For the FreeHDL package to operate correctly the directory where the software is installed must be included in the shell PATH from which Qucs is launched.

$<sup>^{24}{\</sup>rm The}$  value change dump language was originally designed as a simulation waveform interchange format for Verilog HDL. The specification of the VCD format can be found at http://www-ee.eng.hawaii.edu/ msmith/ASICs/HTML/Verilog/LRM/HTML/15/ch15.2.htm

Figure 22: Detailed flow diagram showing VHDL code compilation and simulation results processing.

### VHDL predefined packages and libraries.

All VHDL language processing systems provide a predefined VHDL package called standard. This package defines many of the fundamental VHDL data types, for example bit, character, integer and real. The predefined types, subtypes and other functions in the package standard are stored in a library called STD. The FreeHDL version of library STD includes an additional VHDL package called textio which is used to input and output signal data from and to files. A second library called IEEE defines (1) multivalued logic signals defined by nine different encoding values, making it possible to model digital circuits that are composed from different technology components, (2) logic signal subtypes and (3) an extensive range of useful functions, procedures and overloaded operators. The FreeHDL version of the IEEE library consists of the following packages:

- 1. std\_logic\_1164

- 2. numeric\_bit

- 3. math\_real

- 4. numeric\_std

- 5. std\_logic\_arith

- 6. std\_logic\_unsigned

- 7. vital\_timing

One other library is always defined by VHDL code processing systems namely the work library. This library holds user compiled VHDL entity/architecture design units.

#### VHDL simulation code structures.

In its most basic form VHDL circuit simulation code is structured as an entityarchitecture test bench which includes input signal test information.<sup>25</sup> An example outline of the basic format is

```

entity testbench is

--- entity body statements

end entity testbench;

---

architecture behavioural of testbench is

--- architecture body statements

end architecture behavioural;

```

$<sup>^{25}\</sup>mathrm{Test}$  signals are often called test vectors.

VHDL data types, functions and operators in package standard are always visible to VHDL test bench code and reference to their use need not be added explicitly. However, if the test bench entity-architecture uses data types or other items defined in other libraries, for example the std\_logic type in the IEEE library, then reference to them needs to be added before each entity-architecture pair where they are used. Libraries are referenced using the VHDL *library* and *use* statements. An example showing how these statements are employed is outlined in the following VHDL code segment:

```

library ieee;

use ieee.std_logic_1164.all;

---

entity testbench is

--- entity body statements

end entity testbench;

---

architecture behavioural of testbench is

--- architecture body statements

end architecture behavioural;

```

Here the VHDL code word *all* signifies that all items in a specific library are to be made available for use in the following entity/architecture pair; testbench in the above example. If more than one library is to be used then a library/use statement is needed for each library reference. Most complete VHDL circuit simulation programs consist of more than one entity/architecture pair. In such cases the circuit test bench, with its signal test vectors, must be the last entry in the program. An example of a more complex VHDL program structure is

```

library ieee;

use ieee.std_logic_1164.all;

---

entity comp1 is

--- entity body statements

end entity comp1;

---

architecture behavioural of comp1 is

--- architecture body statements

end architecture behavioural;

---

library ieee;

use ieee.std_logic_1164.all;

---

entity comp2 is

--- entity body statements

```

end entity comp2; --architecture behavioural of comp2 is --- architecture body statements end architecture behavioural; --library ieee; use ieee.std\_logic\_1164.all; --use work.all; --entity testbench is --- entity body statements end entity testbench; --architecture behavioural of testbench is --- architecture body statements end architecture behavioural;

During the conversion of VHDL code to a machine code simulation program each entity/architecture pair, prior to the final test bench entry, is compiled as a separate design unit and stored in the work library<sup>26</sup>. Compiled design units held in the work library can be referenced in other entity/architecture models provided the VHDL statement *use work.all*;<sup>27</sup> is inserted in the VHDL simulation code prior to each entity/architecture statement where they are referenced.

$<sup>^{26}</sup>$ The testbench entity/architecture pair is also, of course, compiled but this design unit is the one that is run as the executable simulation program.

$<sup>^{27} {\</sup>rm References}$  to individual items are also allowed by inserting, for example, use.work.comb1; use.work.comb2; in the VHDL code.

#### VHDL data types.

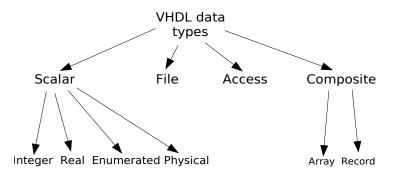

Figure 23: VHDL data types

The chart shown in Fig. 23 indicates the different data types that are available in the VHDL language. FreeHDL implements all these data types. In practical circuit simulation the different VHDL data types are normally used to specify (1) signals, (2) variables and (3) constants<sup>28</sup>. During simulation Qucs/FreeHDL automatically stores the values of integer, real and enumerated bit signals as simulation time progresses. Furthermore, bit\_vector and IEEE signal types including std\_logic\_vector are also stored. Signals of these types are then available for plotting and tabulation using the Timing, Truth table, Tabular and Cartesian output diagrams. Selected elements in user defined composite signals, those that are stored in arrays for example<sup>29</sup>, can be assigned to the basic signal types then displayed.<sup>30</sup>. An example of how this is done is given in later sections of these update tutorial notes. Note - the values of variables and constants are not recorded during simulation.

<sup>&</sup>lt;sup>28</sup>Type file is of course different in that it is used to store either test vectors, component data such as ROM contents and output simulation results.

<sup>&</sup>lt;sup>29</sup>Please note that signal types based on the composite type record will probably cause the Ques simulation cycle to fail - work on this data type has been added to the to-do list.

<sup>&</sup>lt;sup>30</sup>Qucs/FreeHDL also automatically collects waveform data for composite signals based on arrays of bit and IEEE signal types. However, in the case of large arrays care is needed when plotting or tabulating these directly because the entire contents of an array is output each time a signal is displayed.

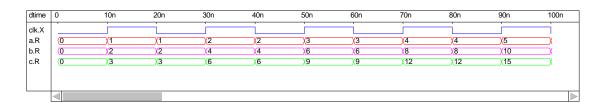

#### An example VHDL simulation employing integer signals.

The following VHDL code demonstrates how the integer data type can be used to represent signals. In this example signals A, B change state on the rising edge of clock clk. The code tests the addition of integer signals and constants using arithmetic operators defined in library STD.<sup>31</sup> The results from this simulation are shown in Fig. 24.

```

--- A very basic test of data type integer.

entity testbench is

end entity testbench;

architecture behavioural of testbench is

signal A, B, C : integer := 0;

signal clk : bit;

begin

p0 : process is --- Generate clock signal.

begin

clk <= '0';

wait for 10 ns;

clk <= '1';

wait for 10 ns;

end process p0;

p1 : process (clk) is

begin

if (clk'event and clk = '1') then

A \le A + 1;

B \le B + 2;

end if;

end process p1;

C \leq A + B;

end architecture behavioural;

```

Figure 24: Output results for a simple test bench example employing integer signals.

$<sup>^{31}{\</sup>rm The}$  specification for the FreeHDL library STD can be found in text file freehdl- $0.0.3/{\rm std/standard.vhdl}.$

## Multivalued logic.

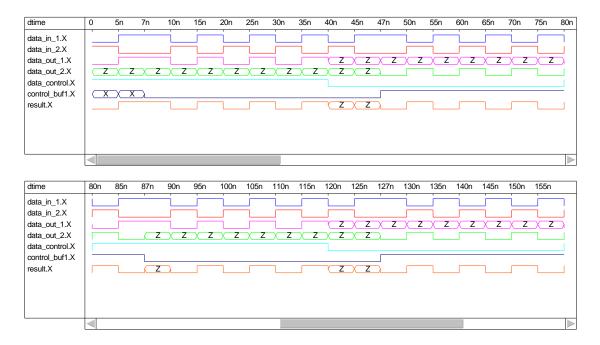

Although signal types bit and bit-vector are widely employed when simulating digital systems one of their great weaknesses is the fact that it is difficult to represent signal bus systems simply using only logic '0' and logic '1' signal encoding. Moreover, circuits where bus signal contention occurs often result in simulation failure. The IEEE std\_logic\_1164 package overcomes this limitation through the introduction of a multivalued logic system which defines nine different logic values to represent signal types and signal strengths. Not only is the bus contention problem solved through logic resolving functions but the multivalued logic system allows devices constructed from different manufacturing technologies to be simulated at the same time, ensuring that the simulation process mirrors real circuit design practices. The next two simulation examples introduce the nine value logic system and demonstrate it's use in the design of digital bus systems. Signals of type real are also introduced to show their representation by Ques. Listed below is the VHDL code for a basic simulation which generates a set of IEEE std\_logic, integer and real signals. Figure 25 illustrates how the Ques Timing diagram displays different signal types. A section of tabulated results are also given in Fig. 26.

```

library ieee;

use ieee.std_logic_1164.all;

entity testbench is

end entity testbench;

architecture behavioural of testbench is

signal clk : bit;

signal bv1 : bit_vector(8 downto 0);

signal stdl1 : std_logic_vector(8 downto 0);

signal INT1 : integer := 0;

signal INT2 : integer := 99;

signal R1 : real := 0.33;

signal R2 : real := 99.0;

signal R3 : real := 0.0;

signal R4 : real := 0.0;

begin

p0 : process is

begin

clk <= '0'; wait for 10 ns;

clk <= '1'; wait for 10 ns;

end process p0;

```

```

p1 : process(clk) is

variable v1 : integer := 0;

begin

if (clk 'event and clk = '1') then

v1 := v1+1;

case v1 is

when 1 => bv1 <= "000000000"; stdl1 <= "000000000";

when 2 => bv1 <= "000000001"; stdl1 <= "000000001";

when 3 \implies bv1 \le "000000011"; stdl1 \le "00000001X";

when 4 => bv1 <= "000000111"; stdl1 <= "0000001XZ";

when 5 => bv1 <= "000001111"; stdl1 <= "000001XZU";

when 6 \implies bv1 \le "000011111"; stdl1 \le "00001XZUW";

when 7 \implies bv1 \iff "0001111111"; stdl1 \iff "0001XZUWL";

when 8 \implies bv1 \iff "0011111111"; stdl1 \iff "001XZUWLH";

when 9 => bv1 <= "111111111"; stdl1 <= "01XZUWLH-";

when others \Rightarrow v1 := 0;

end case;

end if;

end process p1;

p3 : process (clk) is

begin

if (clk 'event and clk = '1')

then

INT1 \leq INT1 + 1;

INT2 \leq INT2 -20;

end if;

if(INT1 \ge 9) then

INT1 \leq 0;

INT2 <= 99;

end if;

end process p3;

p4 : process (clk) is

Variable V2 : real;

begin

if (clk 'event and clk='1')

\mathbf{then}

R1 \le R1 + 1.0;

R2 <= R2 - 20.0;

R3 <= R1*R2;

R4 \le R2/(R1+0.0001);

end if;

if(R1 \ge 20.0) then

```

$\begin{array}{rll} {\rm R1} \; <= \; 0\,.\,0\,; \\ {\rm R2} \; <= \; 9\,9\,.\,0\,; \\ {\rm end} \; \; {\rm if}\,; \end{array}$

end process p4;

end architecture behavioural;

| clk.X                                                             |                                                   | 10n                                                    | 20n                                                 | 30n                                                                   | 40n                                              | 50n                                                   | 60n                                               | 70n                                 |